- Boucle à phase asservie

-

Une PLL (de l'anglais « Phase-Locked Loop »), ou boucle à phase asservie, ou encore boucle à verrouillage de phase[1], est un montage électronique permettant d'asservir la phase instantanée de sortie sur la phase instantanée d'entrée, mais elle permet aussi d'asservir une fréquence de sortie sur un multiple de la fréquence d'entrée.

Historique

L'invention de la boucle à verrouillage de phase est actuellement attribuée à un ingénieur Français, Henri de Bellescize, en 1932.

Etant donné que la réalisation des circuits correspondants est assez complexe et demande plusieurs dizaines de composants, ce n’est que dans les années 1960, avec l'apparition des circuits intégrés que la mise en œuvre de l'invention s'étend de façon considérable.

Descriptif de la PLL

Structure

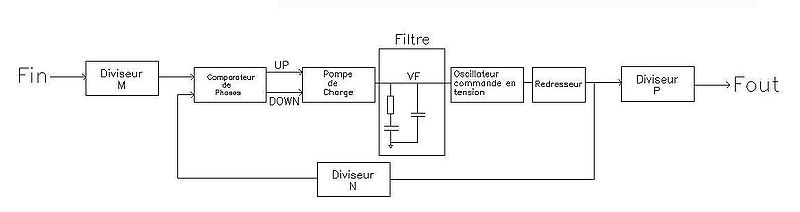

Une boucle à verrouillage de phase classique est constituée :

- d'un comparateur de phase (Phase Frequency Detector - PFD),

- d'une pompe de charges (Charge Pump - CP),

- d'un filtre de boucle,

- d'un oscillateur contrôlé en tension (Voltage Controlled Oscillator - VCO) et

- d'un diviseur de fréquence.

On le trouve également sous la forme d'un composant électronique.

Schéma du système

Relation entre fréquence d'entrée et fréquence de sortie : Fout = Fin * N / (MP)

Principe de fonctionnement

Ordre de la PLL

L'ordre de la PLL est égal au nombre de pôles de la fonction de transfert qui est égal à l'ordre du filtre + 1. Par exemple, pour un filtre d'ordre 1, la PLL est d'ordre 2. Pour un filtre d'ordre 2, la PLL est d'ordre 3. Des exemples de filtre sont donnés ci-dessous.

Fonction de Transfert

Stabilité

Types de PLLs

- PLL logicielle.

Eléments

Oscillateur contrôlé en tension

L’oscillateur contrôlé en tension (VCO – Voltage Controlled Oscillator) a pour fonction de générer un signal périodique dont la fréquence est proportionnelle à la tension appliquée sur son entrée.

Détecteur / Comparateur de Phase

Le détecteur ou comparateur de phase doit fournir, après filtrage, une tension continue (ou lentement variable) proportionnelle à l'écart de phase existant entre les signaux d'entrée et de retour de boucle.

Filtrage

Le filtre sert à :

- Stabiliser la boucle de contre-réaction.

- Filtrer les éléments de bruit intrinsèques.

- Faire la moyenne de la tension de sortie du comparateur de phase.

Diviseur de fréquence

Un diviseur de fréquence par N multiplie la fréquence de sortie de la PLL par N

Interface de sortie

Applications

Démoduler un signal radio-fréquence

Dans les récepteurs radio-fréquence, un signal électromagnétique modulé suivant un certain protocole (FSK, GMSK, QAM64...) génère une force électromotrice dans l'antenne, qui est convertie en un signal électrique amplifié et filtré. Ce système utilise notamment une fréquence de référence appelée la LO (local oscillator), qui est générée par une boucle à verrouillage de phase.

Retrouver la fréquence porteuse d'un signal

C'est le cas par exemple dans le cadre de la démodulation radio FM ou AM. Un poste radio contient une PLL dont on fait varier le filtrage du signal d'entrée. Ce signal filtré pilote ensuite la PLL, qui se cale sur cette fréquence durant ce que l'on appelle la phase d'accrochage, et génère ensuite en sortie le signal démodulé.

Multiplier une fréquence d'horloge

Souvent les systèmes numériques requièrent une fréquence interne de travail importante, de l'ordre de plusieurs centaines de mégahertz. En général un cristal oscillateur piézoélectrique sert de référence car il génère une gigue d'horloge très faible. L'inconvénient du cristal est que souvent sa fréquence est basse, de l'ordre de 20 MHz à 30 MHz, et qu'il est nécessaire de multiplier sa fréquence par un facteur K afin de générer l'horloge du système numérique. C'est le rôle de la PLL.

Gigue

Sources de bruit extrinsèques

Le signal d'entrée présente un certain facteur de qualité en termes de bruit caractérisé par une gigue temporelle ou par un bruit de phase. Par exemple, si la fréquence d'entrée provient d'une horloge de sortie venant d'un autre système, il contient un bruit qui va être filtré et amplifié par la PLL. Il est donc nécessaire de bien comprendre le gabarit en bruit du signal d'entrée afin d'assurer une certaine qualité d'horloge en sortie. Actuellement, les meilleures sources d'horloge de référence d'entrée sont les quartz oscillateurs et servent en général pour les PLL qui requièrent un minimum de qualité en entrée. Il est important de comparer chez les constructeurs de quartz les qualités respectives en bruit de phase afin de faire le bon compromis entre le prix du quartz et le facteur de qualité de la référence en fonction de ce que la spécification en sortie nécessite.

Sources de bruit intrinsèques

Les sources de bruit intrinsèques sont liées aux éléments de la PLL, que ce soient les résistances ou les transistors. Les différents bruits à prendre en compte sont le bruit thermique, le bruit de Flicker, le bruit grenaille, le bruit de pop corn, le bruit quantique... L'étude de ces bruits intrinsèques se fait de la manière suivante :

- On élabore un modèle linéaire de la PLL que l'on implémente sous un simulateur, par exemple SPICE ;

- on simule le bruit de phase de chaque sous-bloc ;

- on implémente ces bruits de phase dans le modèle linéaire de la PLL, pour en extraire en sortie le bruit de phase total de la structure.

Parasites intrinsèques

Les impuretés relèvent du domaine de tout processus non stochastique (aléatoire) qui se rajoutent au signal voulu.

Une PLL consomme un courant qui présente des pics en courant, qui par l'intermédiaire des chutes de tension sur Silicium ou sur la plaque de test, se traduisent par des pics de tension sur les Alims de la PLL. Ces pics de tension génèrent alors une dégradation de la qualité de du signal de sortie et ces impuretés peuvent facilement être observées en temporel sur les alimentations à l'aide d'un oscilloscope, ou sur le signal de sortie à l'aide d'un analyseur de spectre. Le concepteur de PLL veillera donc tout particulièrement au routage sur carte et sur silicium de la PLL.

De plus, les capacités du filtre de boucle ne sont pas parfaites et un léger courant de fuite passe à travers chacune de ces capacités. Ce courant génère une chute de tension modulée à la fréquence d'entrée qui se traduit en sortie de la PLL par des fréquences parasites. Ainsi donc le développeur tiendra compte de ce point, par exemple en microélectronique ce courant de fuite est directement proportionnel à l'épaisseur d'oxyde capacitive et à la taille de la capacité.

Parasites extrinsèques

Les impuretés extrinsèques sont des fréquences parasites qui viennent de l'extérieur et qui ne sont pas produites par la PLL elle-même. Par exemple des fréquences électromagnétiques externes, des fréquences sur la tension d'alimentation mal filtrée sont traitées par la PLL et la qualité de l'horloge de sortie en dépend. C'est pourquoi pour certaines applications nécessitant une bonne qualité de sortie, il est requis un blindage de la structure, et de travailler la phase compatibilité électromagnétique de la PLL dans le système électronique.

Bruit de Phase

Gigue Temporelle

Points de spécification

Fréquence d'entrée

Oscillateur cristal

En général, l'horloge d'entrée provient d'un oscillateur cristal (à quartz) qui génère un signal de référence extrêmement peu bruité. Ce cristal est mis en résonance par l'intermédiaire d'un module interne à la puce et dont le bruit devra être évalué. L'avantage d'un tel système est une référence peu bruitée, mais la fréquence des cristaux est relativement basse, de l'ordre de la dizaine de MHz. Typiquement, les cristaux les plus utilisés sur le marché fonctionnent à 24 MHz.

Fréquence d'entrée faible

Pour une fréquence de sortie donnée, plus la fréquence d'entrée est faible, plus le facteur de multiplication de la boucle est important. Une étude du système prouve que plus ce facteur est important, plus la taille du filtre de boucle nécessaire à la stabilisation du système est importante.

Fréquence d'entrée élevée

L'entrée de la PLL peut très bien être une sortie d'une autre PLL et être par conséquent élevée. Dans ce cas, pour une même fréquence de sortie, le facteur de multiplication de boucle est réduit et le filtre de stabilisation de boucle sera relativement faible. Cependant, l'horloge d'entrée est plus bruitée qu'un simple cristal oscillateur, et une étude précise de la transmission du bruit entre l'entrée et la sortie doit être effectuée afin de déterminer si le système complet répond bien aux exigences de spécification.

Fréquence de sortie

Bruit de Phase

Jitter temporel

le rapport cyclique

Le rapport cyclique est un facteur de spécification important :

- en numérique :

Il spécifie la demi-période minimum (sans inclure la gigue) pendant lequel les portes logiques vont pouvoir basculer. Une spécification typique de rapport cyclique pour le numérique est de 55 % / 45 %.

- en analogique mixte :

Le rapport cyclique peut être un facteur direct sur la qualité de sortie, selon l'architecture de démodulation. Dans ce cas, la spécification sur le rapport cyclique est beaucoup plus restrictive et une méthode classique pour obtenir un bon rapport cyclique est de générer le double de la fréquence escomptée et ensuite de la diviser par une simple bascule: on obtiendra des rapports cycliques de l'ordre de 49 % à 51 %

- en analogique RF :

Pour des signaux carrés, un rapport cylique performant est nécessaire, mais il arrive souvent que le système RF nécessite une horloge non pas carrée, mais sinusoïdale. Pour cette dernière, le rapport cyclique n'est plus un critère de spécification.

Consommation en mode de fonctionnement

La consommation de la PLL dépend de divers facteurs tels que :

Consommation du VCO : en général, la consommation du VCO est inversement proportionnelle au bruit généré par l'oscillateur. Ce facteur de proportionnalité dépend du type d'oscillateur. Par exemple, un oscillateur LC aura un coefficient plus faible qu'un oscillateur en anneau. De plus, la consommation du VCO dépend de la fréquence d'utilisation de la PLL. Plus la fréquence augmente, plus la consommation est élevée. En conclusion, une PLL qui travaille à haute fréquence avec un besoin de petite gigue ou faible bruit de phase consommera jusqu'à plusieurs milliampères.

Consommation du buffer de sortie :

La PLL va conduire en signal d'horloge un système numérique. La consommation de ce buffer est directement proportionnelle à la charge capacitive en pF en sortie et à la fréquence d'horloge. Cette consommation peut aller à plusieurs mA pour des fréquences d'horloge de plus de 1 GHz, pour une charge de l'ordre de 200 fF à 500 fF.

Consommation en mode éteint

Facteur de multiplication

Temps de Mise en route

Temps de Mise en arrêt

Notes

- Michel Fleutry, recommande « boucle à phase asservie » dans son Dictionnaire encyclopédique de l'électronique – anglais / français, (ISBN 2-85608-043-X))

- Portail de l’électricité et de l’électronique

Wikimedia Foundation. 2010.